# JOURNAL

**JULY 1987**

July 1987 Volume 38 • Number 7

# JOURNAL

### Articles

4 Dedicated Display Monitors Digital Radio Patterns, by David J. Haworth, John R. Pottinger, and Murdo J. McKissock An end-on-view, or constellation, of the waveforms making up a digital radio signal provides a graphic display of the effects of several impairments.

#### **11 Automated Timing Jitter Testing**

**13** Constellation Measurement: A Tool for Evaluating Digital Radio, by Murdo J. McKissock Statistical analysis of displayed constellation clusters helps determine digital radio impairments.

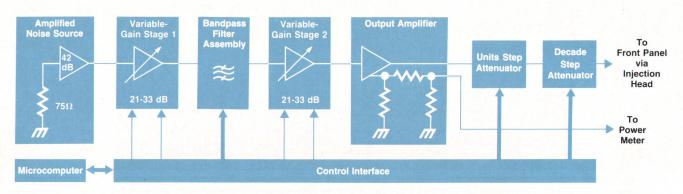

**19** A Digital Radio Noise and Interference Test Set, by Geoffrey Waters Establishing accurate carrier-to-noise ratios and interference levels is a necessary part of measuring bit error rate.

22 Noise Crest Factor Enhancement23 Noise Bandwidth Measurement

26 Microprocessor-Enhanced Performance in an Analog Power Meter, by Anthony Lymer A custom thermal converter and an autozero circuit are key design components.

**30** An Accurate Wideband Noise Generator and a High-Stability Reference Source, by Dayananda K. Rasaratnam These modules make it possible to adjust the injected noise level automatically to maintain a desired carrier-to-noise ratio.

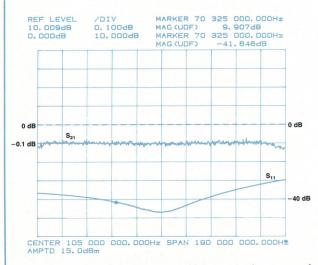

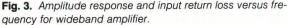

33 General-Purpose Wideband Thick-Film Hybrid Amplifier

**36** Automated Radio Testing Shortens Test Time and Enhances Accuracy, by John A. Duff This system can reduce the time required to measure flat fade performance by 60 to 90 percent.

38 A Reusable Screen Forms Package

#### **Departments**

- 3 In this Issue

- 3 What's Ahead

- 18 Authors

Editor, Richard P. Dolan • Associate Editor, Business Manager, Kenneth A. Shaw • Assistant Editor, Nancy R. Teater • Art Director, Photographer, Arvid A. Danielson Support Supervisor, Susan E. Wright • Administrative Services, Typography, Anne S. LoPresti • European Production Supervisor, Michael Zandwijken

#### In this Issue

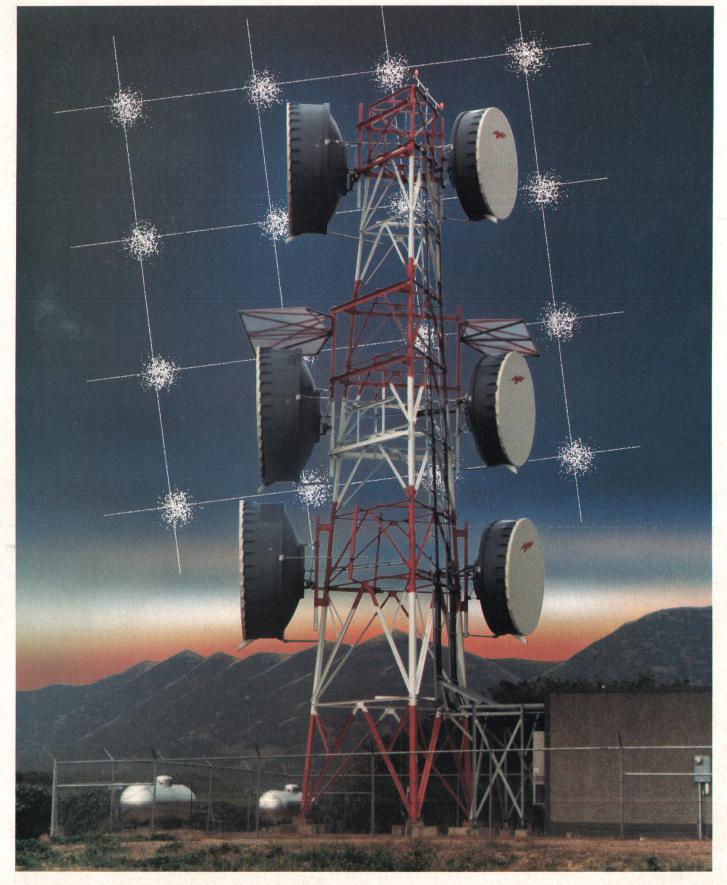

Behind many of the microwave antenna towers one can see riding the tops of ridges and tall buildings are digital radio systems, that is, systems in which the information is imposed on the microwave carrier signal by digital modulation techniques. Two instruments for testing digital radios are the subjects of this issue.

One important measure of the performance of a digital radio is the bit error rate, or BER. What portion of the data bits being transmitted can be expected to be corrupted by noise? One in a million? One in ten million? The answer depends, as one might expect, on typical radio conditions like

fading and interference. If the carrier power fades by as little as 10%, the BER can get ten times worse. The HP 3708A Noise and Interference Test Set is designed to inject precise amounts of noise and interference into a digital radio so the effect on the radio's BER can be measured. The design and theory of operation of this instrument are presented in the papers on pages 19, 26, and 30, and on page 36 is a description of an automatic test system for BER tests of digital radios in production. Among the engineering challenges faced by the HP 3708A's designers were how to maintain a precise carrier-to-noise power ratio when the carrier power is changing, how to guarantee that the noise has not only the required power level but also high enough peaks to approximate real noise, and how to get both fast response and high accuracy in microwave power measurements.

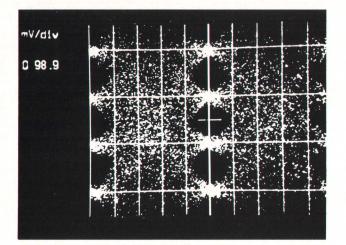

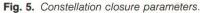

There are many different digital modulation techniques in use today. They have names like QPSK, 49QPR, and 64QAM, where the Q stands for quadrature. The modulation signal has two components, called in-phase (I) and quadrature (Q), each of which can assume only a finite number of values and will have exactly one of these values when the receiver samples the signal. In 64QAM, for example, which means 64-state quadrature amplitude modulation, I and Q can each take on eight values ( $8 \times 8 = 64$ ). If you were to plot the I and Q values received in such a system, the plot should look like a regular 8×8 grid of 64 dots. Because of noise and other impairments, an I-versus-Q plot for a real digital radio more often consists of clusters of dots, and the grid may be distorted. The nice thing is that you can tell a lot about how the radio is performing by looking at such a plot, which is called a constellation diagram. There's one on the cover, and you'll find others in the papers on pages 4 and 13, which describe the design of the HP 3709A Constellation Display. This special-purpose display adapts to various digital modulation schemes at the flip of a switch, and not only displays the constellation diagram but also computes statistics of the dot clusters and various distortion parameters. Among the design challenges were how to minimize timing jitter in the sampling circuit and how to deal with display distortion, which can mimic distortion in the digital radio.

-R. P. Dolan

## What's Ahead

The design and development of the HP-18C and HP-28C, HP's latest handheld calculators for business and technical professionals, are the subjects of the August issue.

The HP Journal encourages technical discussion of the topics presented in recent articles and will publish letters expected to be of interest to our readers. Letters must be brief and are subject to editing. Letters should be addressed to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304, U.S.A.

# Dedicated Display Monitors Digital Radio Patterns

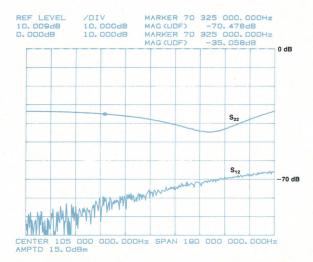

One way of displaying the complex waveforms generated in digital radio systems is the constellation display, a method that allows rapid visual evaluation of a system's performance.

### by David J. Haworth, John R. Pottinger, and Murdo J. McKissock

HE HP 3709A CONSTELLATION DISPLAY (Fig. 1) is a specially engineered two-channel sampling oscilloscope for monitoring the eye and constellation patterns in a digital radio. Although called digital radio because the input is digital, much of the circuitry is analog and the design of a digital radio is an exercise in high-performance analog and digital design. The waveforms are random multilevel wideband signals, and require a highperformance sampling oscilloscope to display them. The HP 3709A design goals were high performance, low cost, ease of use, quality, and manufacturability.

Because the instrument is dedicated to one application, it has some novel features such as user-selectable graticules and dedicated constellation measurements. Many of the controls have been simplified for easier use. The time base autoranges to display two complete cycles of the input waveform. The usual trigger and trigger mode controls are not necessary because the instrument triggers from a clock waveform supplied by the radio. The samplers have been optimized for use on random signals and do not have the dot response problems of earlier sampling oscilloscopes.

A choice of internally generated graticules can be selected by a rear-panel switch to correspond to commonly used modulation schemes: QPSK, 9QPR, 16QAM, 49QPR, and 64QAM (see references 1 through 4 for discussions of these modulation methods and other digital radio fundamentals). For 16QAM, a  $4 \times 4$  graticule is displayed and for 49QPR, a  $7 \times 7$  graticule is displayed. Alphanumeric

information is also presented to display instrument status, self-test messages, and results of the dedicated measurements. A hard copy of the constellation can be output by the HP 3709A on an HP ThinkJet Printer via the HP-IB (IEEE 488/IEC 625). See Fig. 9 on page 17 for a sample printout.

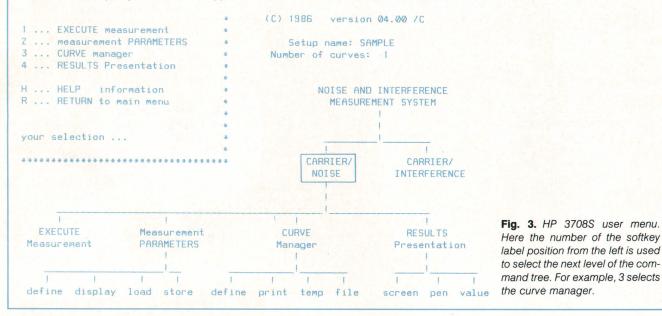

The two input channels are labeled I (in-phase) and Q (quadrature) instead of Channel A and Channel B because this is how the typical customer refers to the two radio channels.

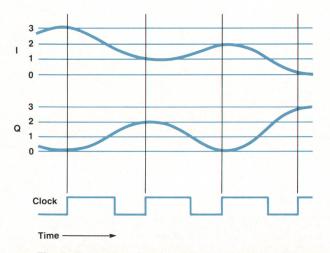

There are four modes: constellation, I eye, Q eye, and measure, selected directly by dedicated keys. In eye mode the HP 3709A operates as a conventional oscilloscope with volts indicated on the Y axis and time base sweep on the X axis. A typical eye diagram is shown in Fig. 2. Constellation mode is what some oscilloscopes label A versus B. This mode displays a sampled instant of the I signal on the X axis and the Q signal on the Y axis. In this mode there is no time base sweep, the same point on the waveform is sampled every time, and timing jitter performance must be good.

The displayed I and Q signals are controlled by a group of dedicated controls whose sensitivity is displayed on the CRT. The samplers are calibrated every three minutes to eliminate gain and offset errors. A delay control allows the user to move the sampling instant to the position of maximum eye opening. The two data inputs are normally sampled at the same instant, but two additional delays can

**Fig. 1.** *HP* 3709A Constellation Display.

**Fig. 2.** Eye diagram viewed on an HP 3709A. Looking grainy because the display is sampled, the eye is in the center with a bright line marker.

be enabled to move the sampling instants independently. A trigger edge select key completes the user controls.

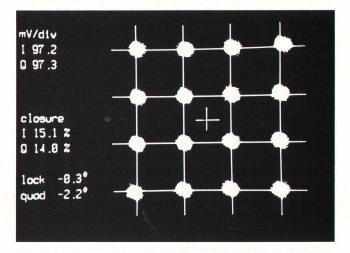

Fig. 3 shows the baseband signals and symbol clock for a typical modulation scheme, 16QAM. The signals are sampled at instants defined by the symbol clock generated within the digital radio receiver. The I and Q signals have discrete values when the active edge of the clock occurs. The eye has four discrete levels at the correct sampling instant for 16QAM signals. An ideal constellation is a single point for each modulation state and the whole pattern is aligned to the graticule. However, the typical constellation (Fig. 4) shows clusters instead of points because of imperfections in the radio. Similarly, the eye diagram is not a single line but many overlapping lines generated by the distortion of the data flowing through the radio.

Usually there are impairments causing small amounts of noise and geometric distortions of the constellation. The

**Fig. 3.** Typical baseband and symbol clock waveforms for a 16QAM radio system. The two channels, I and Q, have four possible states: 0, 1, 2, and 3. The waveforms are filtered to conserve bandwidth, so they look more sinusoidal than square. At the valid edge of the clock (leading edge) the I and Q data will be at one of the four levels.

**MEASURE** key takes 600 samples from the constellation, calculates values for several common impairments, and displays these as numbers on the CRT (see article on page 13). The sampled data is also available over the HP-IB for further analysis by a computer.

#### **Hardware Design**

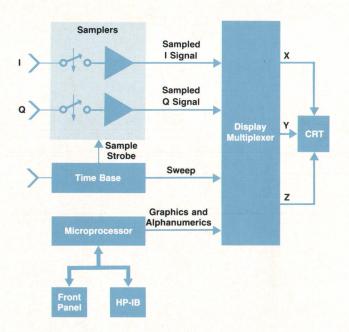

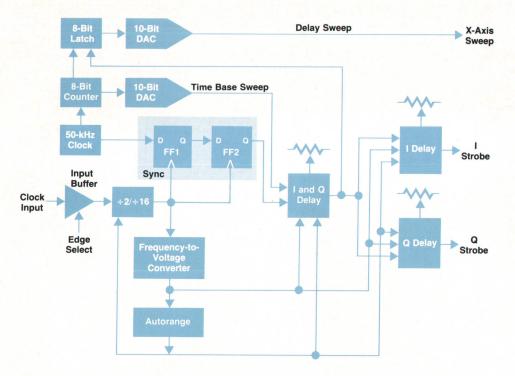

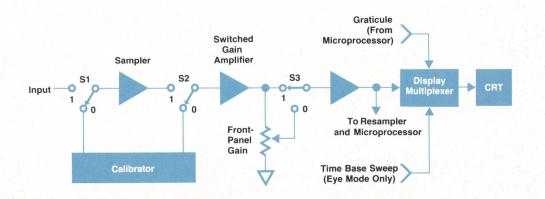

A block diagram of the instrument is shown in Fig. 5. The sample-and-hold circuit is similar to that used in conventional HP sampling oscilloscopes except that it is reset to zero between each sample. Digital radio waveforms are random multilevel signals and viewing these normally requires careful adjustment of a sampling oscilloscope to avoid excessive noise caused by intersymbol interference. By resetting the circuit between samples, the HP 3709A is free of intersymbol interference by design, and therefore is easier to use.

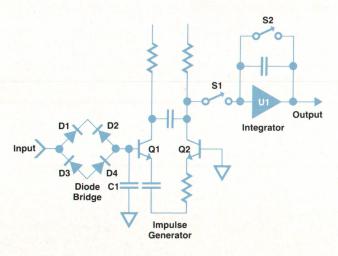

The sample-and-hold circuit consists of a four-diode sampling gate and holding capacitor followed by a stretcher circuit (Fig. 6). The input signal is sampled by switching on diodes D1 to D4 for about 1 ns. The hold capacitor C1 is charged to about 10% of the voltage appearing at the input to the gate. The charge on C1 decays rapidly, but the impulse on the base of Q1 causes an output waveform at its collector proportional in amplitude to the input voltage but stretched in time over several microseconds. The first half cycle of this waveform is integrated and the output of U1 is a voltage proportional to the input voltage. By varying the time switch S1 is closed, the gain can be varied. An autocalibration loop is used to maintain unity gain over a wide temperature range.

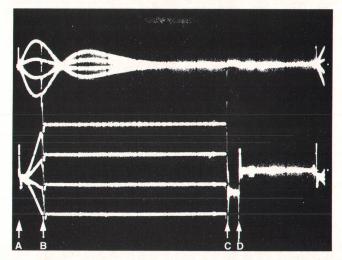

The waveforms in Fig. 7 show the circuit's operation. The input signal is a four-level pseudorandom binary sequence (PRBS) generator which is representative of a digital radio signal. The upper trace is the output of the impulse generator and is a damped resonance proportional in amplitude to the input signal but fixed in frequency. The lower trace is the integrator output.

Time A is when the sample is taken. The signal is then integrated from A to B, during which time S1 is closed. At time B the output of the integrator is equal to the input

Fig. 4. Constellation display on an HP 3709A with measurements of closure, lock angle, and quadrature angle.

Fig. 5. Block diagram of HP 3709A Constellation Display.

voltage and S1 opens, a data valid signal becomes active, and the signal is displayed on screen. The next step resets the integrator to zero volts by closing S2. This happens between times C and D, and the sampler is then ready for the next sample.

In common with many high-frequency analog circuits, the sample-and-hold circuit suffers from drift of gain and offset. Rather than correct all of this in the circuit, a microprocessor-controlled autocalibration loop and a four-channel digital-to-analog converter (DAC) perform the correction. Gain drift is caused mainly by the sample pulse width varying with temperature and is corrected by varying the integration time. Offset drift is caused by diode forward voltage variations in the diode bridge sampling gate and changes in sample pulse shape. Offset correction is applied by varying the bias to the diode bridge. These corrections occur every three minutes unless autocalibration is dis-

Fig. 6. Sampler schematic.

abled via the HP-IB.

#### **Time Base Modes**

The time base operates in three modes: constellation, eye diagram, and calibration mode. The principal elements of the time base circuitry are shown in Fig. 8. A clock input edge is selected every 20  $\mu$ s, delayed by a precise time, and output as the I and Q strobe to the samplers. In eye diagram mode an X-axis time sweep is also generated. The design goal was a CRT display with minimal time base jitter. Since the X axis is quantized to 200 increments over two symbols (two complete cycles), the time between samples is 125 ps at the maximum clock rate of 80 MHz. The jitter specification was set at 30 ps. In practice, the jitter is less (see box on page 11).

Eye Diagram. This mode is the most complex mode, and is similar to conventional sampling oscilloscope operation. There is no time base sweep control. The time base is adjusted automatically to make the display width equal to the width of two symbols for any clock in the range from 1 MHz to 80 MHz. Automatic width control is convenient for comparing eye diagrams. Since they are all displayed the same width, it is easier to pick out impairments. A two-symbol width allows one eye to be placed in the center of the screen, with a half symbol displayed on each side. Two ranges of automatic control are used: 1 MHz to 10 MHz and 8 MHz to 80 MHz. Autoranging handles the range selection. A voltage proportional to the clock input frequency is used to control the gain of the I-and-Q delay (and the I delay and Q delay) one-shot circuits. This voltage also selects either divide-by-2 or divide-by-16 operation via the autorange circuit.

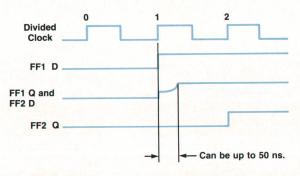

The synchronizer uses two D flip-flops in cascade, both clocked by the divided input clock. The variable divider ensures that all clock inputs are at least 200 ns apart, which ensures that the first flip-flop has settled even if the data and clock change together. The second flip-flop then achieves jitter-free synchronization because its D input is stable long before the second clock edge occurs (see Fig. 9).

**Fig. 7.** Sampler waveforms for a 4-level PRBS input signal. Upper trace is output of impulse generator and lower trace is output of integrator.

Fig. 8. Time base block diagram.

In Fig. 8, the I-and-Q delay allows the user to adjust the sampling instant of both strobes together over a range of one symbol. The I delay and Q delay allow each strobe to be delayed by up to one symbol period. The delay range is independent of the clock rate. The I-and-Q delay is swept by the time base sweep, which has 201 discrete levels. This allows the delay to be stepped progressively through two symbols in 1% steps. The I-and-Q delay function is performed by a monostable (one-shot) circuit designed to have very low timing jitter. This circuit is described later.

The time base sweep is generated by an 8-bit counter driving a 10-bit DAC with states 0 to 54 blanked. This allows 10-bit linearity, approximately 0.1%; the two leastsignificant bits are unused.

In eye diagram mode, a sweep is also required to drive the CRT display. A conventional sampling oscilloscope uses the time base sweep, which requires the sweep to be stable for the duration of the I-and-Q delay, the I (or Q) delay, the sample time, and the display time. The sample rate can be increased if two pipelined sweeps are generated. The first sweep only needs to be stable for the I-and-Q delay time, and the second sweep only needs to be stable while a point is displayed on screen. This allows one point to be displayed while the time base increments to the next point. The X-axis sweep is conveniently generated by latching the time base count and using a second 10-bit DAC.

**Constellation.** In constellation mode the 8-bit time base sweep counter is fixed at the center of the sweep. The display shows the I and Q signals on the X and Y axes. The sample times can still be manually adjusted by the three delay controls.

**Calibration**. In calibration mode, the microprocessor routes the 50-kHz clock directly to the I and Q strobes, so that sampler calibration can be performed even if no clock input is present.

#### Low-Jitter One-Shot Circuit

1

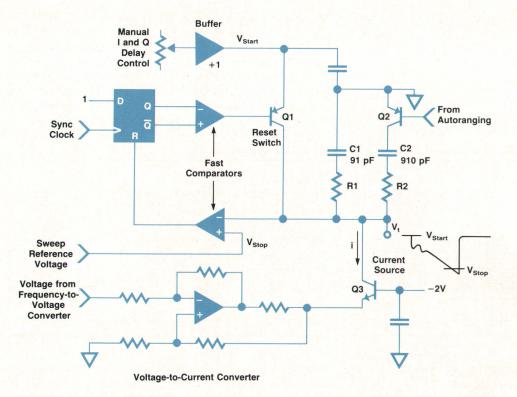

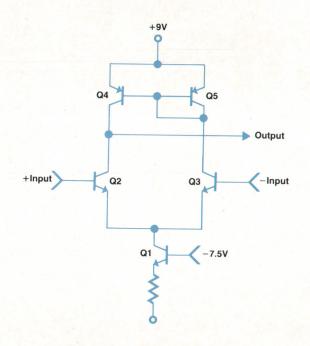

The sampling instant on the HP 3709A is varied with the I-and-Q-delay one-shot circuit (Fig. 10). A discrete circuit was designed because available integrated circuits did not have the required jitter performance.

The one-shot delay time is given by:

$$t = (C1+C2)(V_{Start}-V_{Stop}-iR)/i$$

For frequencies below 10 MHz, C1 and C2 are used; above 10 MHz, only C1 is used.  $V_{Start}$  is set by the user front-panel control.  $V_{Stop}$  is the sweep voltage in eye diagram mode, or a constant value in constellation mode. R represents the effect of R1 and R2, which are added to damp the resonant circuit formed by the timing capacitor and the printed circuit board trace inductance. For C1, a resonant frequency of about 100 MHz is observed. If undamped, the start-up transient would distort the ramp. The current i is supplied by Q3.

The circuit functions as follows. The voltage  $V_t$  at the collector of Q3 is clamped to  $V_{Start}$  initially. When the flip-flop is triggered, Q1 turns off and current supplied by

Fig. 9. Time base synchronizer waveforms.

Q3 causes  $V_t$  to ramp down. When  $V_t$  is more negative than the sweep reference voltage, the flip-flop is reset and Q1 turns on.

The discharging current i is accurately controlled by the voltage-to-current converter operational amplifier. The amplifier is decoupled from the high-speed ramp by the cascode transistor Q3. This configuration allows an accurate current to be maintained despite the high discharge rate. The current source is controlled over a decade range. An additional decade range is provided by switching in the timing capacitor C2 using Q2.

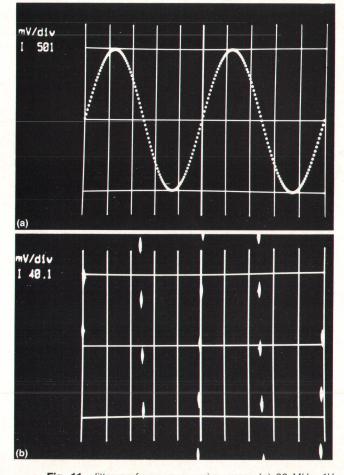

The performance of such a circuit cannot be evaluated by observing the ramp directly at  $V_t$ . Any probe degrades the jitter performance, stray capacitance upsets calibration, and stray inductance causes ringing. Indirect means must be used. The best method is to use the time base to drive the sampler, and sample a sine wave. The zero crossing of a sine wave has a defined dV/dt which allows easy conversion from volts to picoseconds. For example, a 1V peak, 80-MHz sine wave has a dV/dt = 0.503 mV/ps at the zero crossing.

Using a 10-bit analog-to-digital converter after the sampler gives quantization steps of 2 mV for a  $\pm 1V$  input, allowing a time resolution of 2 ps. Linearity is measured by sampling a signal running at twice the clock frequency. Two symbols then contain four cycles or nine zero crossings. Linearity is measured by observing the displacement of the zero crossing. Using this principle, a reliable measurement of jitter and linearity can be achieved in a computer-based test system.

Fig. 11a shows the linearity and jitter performance of the time base one-shot circuit. Fig. 11b shows a residual jitter of approximately 9.5 ps. This value is derived as follows:

80 MHz = 12,500 ps/cycle

Fig. 10. Low-jitter one-shot circuit.

**Fig. 11.** Jitter performance on sine wave. (a) 80 MHz, 1V p-p. (b) Above trace at increased sensitivity, jitter  $\approx$ 9.5 ps.

- 1% of cycle = 125 ps, which corresponds to a displacement of 16.5 mm

- Dot peak-to-peak displacement = 5 mm

- Dot rms displacement  $\approx 5/4 = 1.25$  mm

- Rms jitter  $\approx 125 \times 1.25/16.5 = 9.5$  ps.

However, at lower clock input levels this value increases because of input buffer noise.

#### Analog Signal Processing

After being sampled, the signal is amplified to a suitable level for driving the display. Because the signal is now lower in frequency, this can be done with high-speed op amps. Perhaps the most interesting feature is the hardware multiplexing done to perform several tasks concurrently. The hardware is configured to one of four principal functions by the microprocessor. The various signal paths are (Fig. 12):

- 1. Display the incoming signal

- 2. Display the graticule and text from the microprocessor graphics generator

- Measure the setting of the front-panel gain control, displayed on screen as mV/div

- 4. Measure and correct sampler gain and offset.

The first three functions are implemented with FET analog switches and appear concurrent to the user. The display continuously switches between incoming I and Q data at a 50-kHz rate, the graticule drawing is updated at a 40-Hz rate, and a dc calibration voltage is routed through the front-panel gain control twice per second to measure the setting and thus calculate the instrument sensitivity.

Sampler offset and gain correction normally occurs every three minutes. A three-level dc calibration signal is routed through the sample-and-hold circuit with the front-panel gain control bypassed, leaving only fixed gain stages. The offset is adjusted to zero volts and the gain is adjusted to the value held in ROM. **Resampling and Data Conversion.** Because the output of the sample-and-hold circuit is only valid for 10  $\mu$ s, it is resampled using a slower sample-and-hold circuit to give sufficient time for analog-to-digital (A-to-D) conversion. This conversion is performed by the microprocessor and the DAC using a successive approximation algorithm. The same DAC is used for both graticule generation and measurements, thus reducing errors between the signal on the screen referenced to the graticule and the signal measured by the processor.

#### **Vector Graphics Generator**

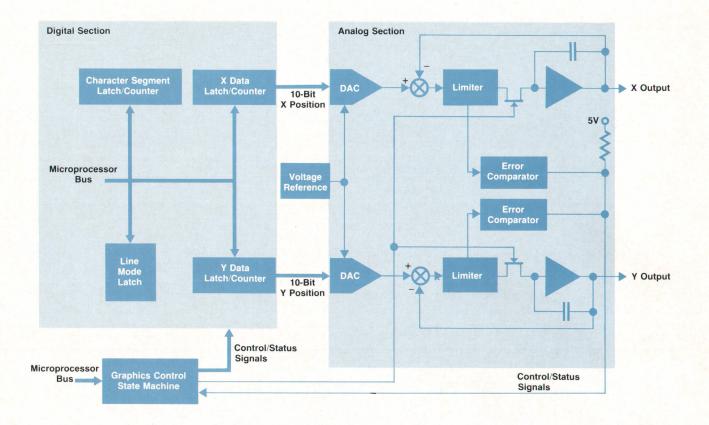

The need for a vector graphics generator was identified early in the design of the HP 3709A Constellation Display. To meet project design goals for low cost and high reliability, circuit complexity had to be minimized. Investigation showed that existing designs offered excellent display quality and plenty of features, but exceeded the target cost by an order of magnitude. Ruthless trimming of unnecessary display features resulted in an efficient design which has a low component count and is easy to manufacture.

The instrument display is an electrostatic CRT module with XYZ vector drive inputs. Graphics are produced by the vector graphic, or calligraphic, technique often used with this type of display. This technique builds a CRT display pattern by modulating the X and Y deflection to draw individual lines and characters. In contrast to a raster scan display, the time needed to refresh the display depends on the number and length of the individual lines (vectors). The technique is used here to generate full-screen graphics in a small fraction of the display time, so that more display time is available for analog data.

The design minimizes cost and board area by tight coupling between the graphics hardware and the main microprocessor. Two DACs are required. With the addition of precision comparators, these DACs are also used to perform

**Fig. 12.** Analog signal processing. Four functions are performed: 1) input signal displayed on CRT (S1 = S2 = 1 and S3 = 0), 2) graticule is displayed on CRT, 3) front-panel gain potentiometer is measured (S1 = S2 = S3 = 0), and 4) sampler is calibrated (S1 = 0 and S2 = S3 = 1).

Fig. 13. Graphics generator block diagram.

analog-to-digital conversion for measurement of constellation samples. By reusing the microprocessor and DACs, the marginal cost of the graphics generator is reduced to only 160 cm<sup>2</sup> of printed circuit board area.

**Display Refresh.** The graphics display is continuously refreshed at a rate of 40 Hz. Although this rate is unusually low, it is sufficient to prevent display flicker with a P39 long-persistence CRT phosphor.

Each refresh cycle starts with a microprocessor interrupt from the real-time clock. This activates the firmware routine that drives the graphics generator. The display is stored internally as a list of primitive operations which represent horizontal lines, vertical lines, hidden moves, or ASCII characters. Line and move operations are sent directly to the graphics generator hardware while ASCII characters are interpreted by the firmware, using table lookup to generate a sequence of line segments for each character.

The display refresh cycle typically uses 5% to 15% of the available display time, and a similar fraction of microprocessor time. Execution speed of the firmware routine is important, so it is coded in assembly language. The inner loops for display list output and character interpretation contain only six microprocessor instructions. This is possible because simultaneous design helped select the best trade-off between hardware and firmware complexity.

Although described as a single operation, display refresh is divided into four phases to even out processor loading and minimize latency for other real-time processes. Two phases are allocated to parts of the graticule and the other two phases are allocated to display text. **Graphics Hardware.** The graphics generator is divided into analog and digital sections, with a state machine to provide control signals. Fig. 13 shows the block diagram.

The analog section generates X and Y signals to drive the display. When drawing a line, these signals must ramp smoothly between the start and end points. If a line is at

Fig. 14. Differential limiter circuit.

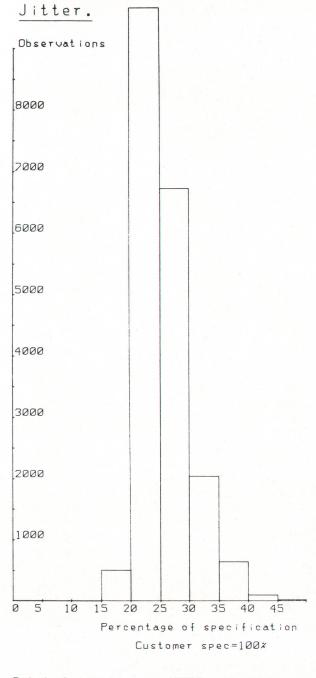

## **Automated Timing Jitter Testing**

Automated testing allows measurement of parameters on every production instrument. In many cases there is virtually no manual method of performing the test in an acceptable time. A good example of this is timing jitter testing. A computer-driven automatic test is the only means of quantifying the amount of timing jitter in the HP 3709A Constellation Display.

The test system's clock input generator is set to the HP 3709A's specified minimum clock input level. This is the condition at which most timing jitter is likely to be seen. A sinusoidal signal is then fed into the I and Q channel inputs from the test system's signal input generator. When the HP 3709A is set to eye mode, two cycles of the signal can be seen. However, the test system is ignorant of the phase of the displayed waveform.

Because the I and Q position controls, which correspond to vertical position controls in eye mode, cannot be switched out, a measurement of the offset is required to be used as a reference for calculating the eye position of zero crossing points and peak points, etc. This is accomplished by switching the signal input generator off (i.e., to its minimum amplitude of approximately -90 dBm, which is approximately 50 dB below the HP 3709A noise floor) and measuring 1000 samples at Eye Position = 0.0000 Sample Periods.

From these 1000 samples, the mean is calculated to give a reference voltage  $V_{\text{ref}}.$  By adjusting the phase of the signal input generator using its minimum phase increment of 0.1 degree, the signal can be set up so that the zero crossing point occurs at Eve Position = 0.0000 Sample Periods. This is the point of maximum slew rate where the worst timing jitter will be observed. By measuring 1000 samples at this point, a distribution of voltage values will be obtained. Using the 1000 samples, the rms value of the voltage at the zero crossing point can be estimated. This rms voltage corresponds to noise at the zero crossing point and has to be converted into the time domain before the timing jitter can be calculated. To calculate the timing jitter from the noise at the zero crossing point, the peak value and frequency of the incoming signal must be known. The peak value is measured by changing the eye position to the peak position of the waveform and measuring the mean value in volts. From this value  $V_{\text{ref}}$  is subtracted to give  $V_{\text{peak}}.$  The frequency is known.

Using the following formula for the instantaneous voltage  $V_i$  of a sine wave, the rms noise can be converted to jitter in the time domain:

$$V_i = V_{peak} \times \sin \omega t$$

where  $\omega=$  frequency in radians/s and t = 1/ $\omega$   $\times$  sin^{-1} (V\_i/V\_{peak}). Therefore:

Timing jitter =  $T_i = 1/\omega \times \sin^{-1} (V_{rms}/V_{peak})$  seconds

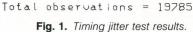

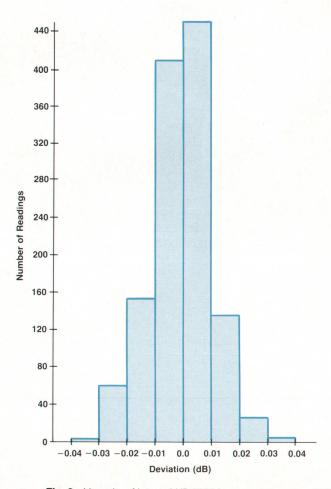

The results obtained during the development phase of the project and the results of the first production instruments were stored on disc. The analysis of the test results calculated the lowest and highest timing jitter values, the mean timing jitter, and the standard deviation at each frequency. This ensured that there were no hidden specification problems. Fig. 1 shows a typical distribution of timing jitter test results.

David Robertson Production Engineer Queensferry Telecommunications Division

3709A CARE TESTING.

an angle to the axes, the X and Y ramp rates must be proportional to the X and Y components of the line so that both signals reach the endpoint at the same time. In a general-purpose vector display the ramp generators are precision circuits since proportionality errors of only 1% are easily visible on a long line. Fortunately it was possible to limit graphics to horizontal lines, vertical lines, and short line segments at 45 degrees to the axes. This made it possible to use the simple ramp generator shown in the diagram.

The analog section operates in three states: idle, hold, and ramp. In the idle state the output of each channel tracks the input. The error signals are small, so the limiters act as simple amplifiers. Overall each channel behaves as a unity-gain buffer with single-pole frequency compensation. In the hold state the FET switches isolate the output integrators. This allows the inputs to be changed to a new graphics position while the outputs remain at the old position. In the ramp state there is a large error between the input and output of one or both channels. The limiter supplies a constant current to the output integrator that causes the output to ramp in the direction of decreasing error. As the error becomes small, the limiter moves into its linear region. Each channel has a pair of comparators which detect position errors that exceed the limiter threshold. For a visible line, the display spot is enabled from the start of the ramp state until the position error signal becomes false, indicating that both channels have returned to the idle state.

At the heart of the circuit is a differential limiter (Fig. 14). This venerable circuit is one of the simplest designs for an op amp input stage. Q1 supplies a constant current to the differential pair Q2 and Q3. Q3's collector feeds the current mirror formed by Q4 and Q5 and the output is added at Q2's collector to give an output current proportional to the differential input voltage. Input voltages of only 100 mV are sufficient to divert all current through one side of the differential pair, providing the limiting action.

The complete circuit for each channel can be likened to an operational amplifier; the integrator amplifier corresponds to the output stage while the integrator capacitor corresponds to the frequency compensation capacitance. The main function of the circuit, the constant rate output ramp, corresponds to one of the least desirable features of an operational amplifier—output slew rate limiting. In this circuit, slew rate limiting is realized with a precision that is not currently available in commercial integrated circuits.

The digital section latches the next graphics position for a line or move operation. For a line segment (ASCII character), it must generate the next position by adding relative segment offsets to the current position. These operations and the idle-hold-ramp-idle sequence for the analog section are controlled by the state machine. The control functions could be performed by the microprocessor, but performance would suffer. The state machine, implemented with a single 20-pin programmable logic device, is an extremely cost-effective solution.

#### **Display Graticule**

An unusual feature of the HP 3709A is the user-selectable

graticule. Depending on the modulation scheme, a constellation display can have clusters arranged in two, three, four, seven, or eight parallel rows and columns. Instead of a fixed display grid, a different graticule is provided for each modulation scheme. These graticules are simpler than a single general-purpose graticule and provide an unambiguous reference position for constellation measurements.

Since the graticule is drawn on the CRT, display imperfections affect the measured constellation and the graticule equally. The operator can use the graticule to resolve small levels of impairment on screen, eliminating any error caused by the CRT. This is important since some constellation impairments are similar to common CRT imperfections. For example, traveling-wave-tube amplitude compression looks very much like CRT barrel distortion.

The graticule generator provides drive signals to the vector display module via a multiplexer, which selects between the sampled analog constellation signals and the graticule. In addition to drawing horizontal and vertical graticule lines, the graticule generator generates display text for the graticule calibration factor, measurement results, and error messages.

#### **Measurement Verification**

The measurements performed by the HP 3709A are complex and involve a combination of hardware and firmware. The three main stages are: sampling and displaying data (hardware), A-to-D conversion (hardware and firmware), and statistics accumulation and analysis (firmware).

The hardware system of the HP 3709A can be checked by applying input signals and measuring accuracy, flatness, noise, et cetera over the HP-IB. However, the dedicated measurements of closure, lock, and quad angle cannot easily be verified in this way. To allow firmware verification, the HP 3709A can accept data over the HP-IB that simulates sampled data from a constellation. A verification program was written on an HP 9000 Series 200 Computer to generate constellations with a variety of impairments for all modulation schemes covered by the HP 3709A. This program checks that the statistics accumulation agrees exactly and the analyses (closure, lock, and quad angles) agree within acceptable limits.

#### **HP-IB Firmware Verification**

A Series 200 BASIC program was written to exercise all the HP-IB commands separately and in sequence. The test program was written around the HP 3709A HP-IB External Reference Specification. This document defines all aspects of the HP-IB behavior of the instrument and is used as a basis for customer documentation. The program is written as a number of modules, each designed to exercise one HP-IB function as thoroughly as possible. Commands with a finite set of parameters are tested for each permissible parameter, while those with infinitely variable parameters are tested at key values (e.g., zero, limits, and just beyond limits) to test error detection and recovery. The modules are executed in a fixed sequence.

The long-term benefit of this approach to interface testing is having a test program to run on any future revisions of HP 3709A firmware.

#### **Product Design**

During the design of the HP 3709A, ease of manufacture was a prime goal. Some of the points considered were:

- 1. Keep the number of printed circuit boards to a minimum. The HP 3709A is made up of only seven printed circuit boards.

- 2. Where possible, choose components that can be inserted in the printed circuit boards by machine to minimize hand loading. 50% of the components in the instrument are inserted automatically.

- 3 Fewer printed circuit boards means that fewer cables are required to interconnect them. There are 13 cables in the HP 3709A: five coaxial, five ribbon, and three simple wire looms. By mounting the processor board against the rear panel we were able to mount the the HP-IB socket and address switch directly on the processor board. The electrical cable from the line power switch was eliminated by putting the switch on the line input board at the rear of the instrument and operating it via a flexible mechanical cable just like a bicycle brake cable. This is purchased as part of the line switch assembly. The advantages of this mechanical cable are that the hazardous line voltages are kept in one small area, and the 50/60-Hz line is not carried through the cabinet with its possible screening problems. This type of cable linkage is less sensitive to mechanical variances than a rigid link would be.

- 4. The preset adjustments and test pins should all be accessible with minimum effort. This was achieved without too much trouble. The only difficulty was providing easy access to the HP 1340A Display Module's X/Y gain, position, and alignment controls. By mounting them along the top edge of the keyboard, we made them accessible through the spare mounting holes in the top of the front frame casting.

#### Acknowledgments

Boyd Williamson did the product definitions for the HP 3709A and was project manager through the early design phase. Peter Roubaud did the operating system and HP-IB firmware. Ross MacIsaac was responsible for the analog gain switching and resampler. Arthur Thornton did the product design and David Robertson was responsible for test software.

#### References

1. H. Walker, "Modulation Schemes and Digital Radio Growth," Microwaves & RF, Vol. 26, no. 2, February 1987, p. 75.

2. H. Walker, "Gauging Errors Set Digital Radio Quality," *Microwaves & RF*, Vol. 26, no. 4, April 1987, p. 89.

3. A Review of Digital Radio Principles and Measurements, Hewlett-Packard Publication No. 5954-7941 (contains parts of references 1 and 2).

4. K. Feher, Digital Communications: Microwave Applications, ISBN 0-13-214080-2.

# Constellation Measurement: A Tool for Evaluating Digital Radio

by Murdo J. McKissock

٩

HE CONSTELLATION DISPLAY is an invaluable tool for alignment and fault diagnosis of digital radios, and an important indicator of the radio's performance margin. The HP 3709A Constellation Display is the first commercial instrument that provides the capability to make quantitative measurements of a constellation.

Measurement data is provided at three different levels: raw samples, statistical accumulations, and analysis results. The raw samples represent individual constellation points and typically might be used to reproduce a constellation on a plotter, or to measure nonconstellation signals. The statistical accumulations provide information on the position, size, and orientation of each display cluster. This forms the basic data for analysis. The analysis results evaluate some common constellation impairments: relative rms cluster size, angle of rotation, and angle of quadrature. Using an external HP-IB (IEEE 488/IEC 625) controller it is possible to use the statistical accumulations to perform

further analysis to measure other constellation impairments such as amplitude compression, amplitude-to-phase conversion, and phase noise.

#### **Raw Constellation Samples**

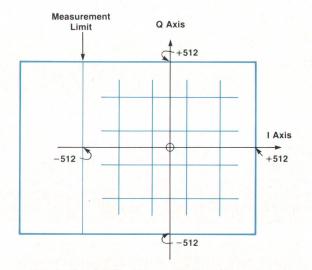

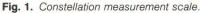

The real-time display is generated from input samples taken at regular intervals. These analog samples drive the display directly. A small proportion of the samples are converted to digital form during a constellation measurement. Each sample has two 10-bit digital values, one each for the in-phase (I) and quadrature (Q) modulation components. Sample values are returned as pairs of integers using the measurement scale illustrated in Fig. 1. A typical measurement might take 1000 digitized samples and plot them to produce a hard copy of the constellation (Fig. 2).

#### **Statistical Accumulations**

Instead of measuring and outputting raw samples, the HP 3709A can process samples internally. For each cluster in the constellation, the instrument accumulates six values:

Fig. 2. Typical constellation plot (1000 samples).

Sum of the products of the I and Q values:  $\sum_{ijk}^{n_{ij}} x_{ijk} y_{ijk}$

where  $(x_{ijk}, y_{ijk})$  is the kth sample in the cluster with I and Q indices i and j.

This is similar to the statistics accumulation occurring in many pocket calculators, but there can be up to 64 sets of 6 registers each, one for each cluster in the modulation scheme.

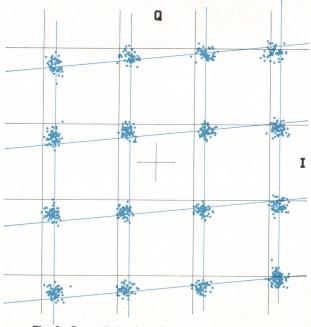

From the register contents, it is easy to compute the mean position, rms size, and correlation coefficient between the I and Q values for each cluster. Fig. 3 shows a plot from a computer program which uses this information to generate ellipses representing Gaussian probability contours.

The individual samples are assigned to a particular "sample bucket" or set of registers using slicing boundaries midway between the constellation graticule lines (Fig. 4). Obviously, the position and overall size of the constellation must be adjusted so there is just one cluster in each of the sample buckets.

When the accumulation is complete, the contents of the registers can be output to an external controller or analyzed by the HP 3709A to obtain measures of constellation impairments.

#### **Analysis Results**

The HP 3709A computes four analysis results:

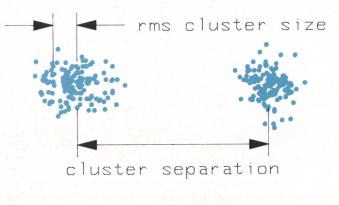

- I and Q constellation closure measures the relative rms cluster size in each direction. Constellation closure = [rms cluster size]/[0.5(cluster separation)]×100% (see Fig. 5).

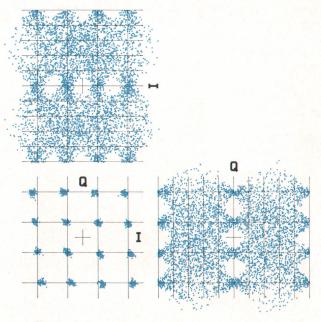

- Lock error measures the angle of rotation between the graticule and the cluster lines. This is related to receiver carrier phase lock error in a digital radio. In Fig. 6, lock error =  $(\theta_1 + \theta_2)/2$ .

- Quad error measures the quadrature error between the cluster lines. Quad error  $= \theta_2 \theta_1$  (see Fig. 6).

Fig. 3. Constellation cluster ellipses.

The results are determined using two separate analysis functions:

- The rms cluster size is estimated, computed as an average over all clusters in the constellation.

- The position, spacing, and slant of the cluster lines are estimated using a least mean squared error (LMSE) estimator to compute the parameters of a suitable model.

The rms cluster size is obtained by assuming that the distribution of points in each cluster is the same. The usual equation for standard deviation is modified to take into account the different mean positions of the individual clusters in the constellation. This gives the equations:

$$s_{x}^{2} = \frac{1}{(N-M^{2})} \sum_{i=1}^{M} \sum_{j=1}^{M} \left[ \sum_{k=1}^{n_{ij}} x_{ijk}^{2} - \frac{1}{n_{ij}} \left( \sum_{k=1}^{n_{ij}} x_{ijk} \right)^{2} \right]$$

$$s_{y}^{2} = \frac{1}{(N-M^{2})} \sum_{i=1}^{M} \sum_{j=1}^{M} \left[ \sum_{k=1}^{n_{ij}} y_{ijk}^{2} - \frac{1}{n_{ij}} \left( \sum_{k=1}^{n_{ij}} y_{ijk} \right)^{2} \right]$$

where M is the number of levels in the modulation scheme. Hence,  $M^2$  is the number of clusters. N is the total number of samples. That is:

$$N = \sum_{i=1}^{M} \sum_{j=1}^{M} n_{ij}$$

The factor (N  $-M^2$ ), sometimes called the number of degrees of freedom, is used instead of N so that the estimate of rms cluster size is unbiased. It represents the total number of samples less the number of cluster mean position values used in the computation. The equations for  $s_x$  and  $s_y$  are designed to give equal weight to all samples to minimize the unavoidable errors caused by random variations in the distribution of samples.

The rms constellation closure for each axis is computed

Fig. 4. Constellation slicing boundaries.

by dividing the rms cluster size  $s_x$  or  $s_y$  by one-half the cluster spacing  $p_{xx}$  or  $p_{yy}$  obtained from the LMSE estimator below:

I closure = 2

$$(s_x/p_{xx})$$

Q closure = 2  $(s_y/p_{yy})$

The term eye closure is often used to express the reduction in the opening of an eye diagram. There is a difference between eye and constellation closure (see Figs. 5 and 7). Constellation closure measures only the size of individual clusters, while eye closure also includes the effect of overlapping clusters in the eye diagram. A feature of the constellation display is that it is possible to resolve separately impairments that cause clusters to overlap in the eye diagram such as lock and quad errors.

The position, spacing, and slant of the cluster lines are estimated using a modeling technique. It is possible to estimate, for example, the spacing from the mean positions of a few clusters. However, this ignores most of the available data so that random errors (measurement variance) in the result will be much larger than necessary. Even the average of all cluster spacings effectively uses only the outer clusters.

Instead, a model constellation is defined. All clusters of the model lie on equally spaced parallel lines. The parameters of the model are the I and Q offsets, I and Q spacings, and I and Q slants. The parameters are computed such that the mean-squared error between the model and the measured constellation samples is minimized. Fig. 8 shows a constellation with mainly linear impairments. Not only is the constellation rotated and out of square, it is slightly offset from the graticule. The best-fit model is shown by the superimposed lines.

The model defines a linear relationship between the I and Q cluster indices and the cluster positions. As a result, the parameters that minimize mean squared error are easily computed from the constellation statistics. The model position of cluster i,j is given by:

$$\hat{\mathbf{x}}_{ij} = \left(i - \frac{M+1}{2}\right) \mathbf{p}_{xx} + \left(j - \frac{M+1}{2}\right) \mathbf{p}_{yx} + \mathbf{p}_{x}$$

$$\hat{y}_{ij} = \left(i - \frac{M+1}{2}\right) p_{xy} + \left(j - \frac{M+1}{2}\right) p_{yy} + p_y$$

The parameters are represented as vectors:

$$\mathbf{P}_{\mathbf{x}} = \begin{bmatrix} \mathbf{p}_{\mathbf{x}\mathbf{x}} \\ \mathbf{p}_{\mathbf{y}\mathbf{x}} \\ \mathbf{p}_{\mathbf{x}} \end{bmatrix} \qquad \mathbf{P}_{\mathbf{y}} = \begin{bmatrix} \mathbf{p}_{\mathbf{x}\mathbf{y}} \\ \mathbf{p}_{\mathbf{y}\mathbf{y}} \\ \mathbf{p}_{\mathbf{y}} \end{bmatrix}$$

The values are computed by solving matrix equations:

$$AP_{x} = B_{x} \qquad \qquad AP_{v} = B_{v}$$

where

$$\mathbf{A} = \sum_{i=1}^{M} \sum_{j=1}^{M} \sum_{k=1}^{n_{ij}} \begin{bmatrix} (i-d)^{2} & (i-d)(j-d) & (i-d) \\ (i-d)(j-d) & (j-d)^{2} & (j-d) \\ (i-d) & (j-d) & 1 \end{bmatrix}$$

$$\mathbf{B}_{\mathbf{x}} = \sum_{i=1}^{M} \sum_{j=1}^{M} \sum_{k=1}^{n_{ij}} \begin{bmatrix} (i-d)x_{ijk} \\ (j-d)x_{ijk} \\ x_{ijk} \end{bmatrix}$$

$$\mathbf{B}_{\mathbf{y}} = \sum_{i=1}^{M} \sum_{j=1}^{M} \sum_{k=1}^{n_{ij}} \begin{bmatrix} (i-d)y_{ijk} \\ (j-d)y_{ijk} \\ y_{ijk} \end{bmatrix}$$

$$d = (M+1)/2$$

Fig. 6. Lock and quad error parameters.

Fig. 7. Constellation and eye diagrams.

Lock and quad errors are computed from the model parameters:

Lock error =

$$\frac{1}{2} [\tan^{-1}(p_{xy}/p_{yy}) - \tan^{-1}(p_{yx}/p_{xx})]$$

Quad error =  $-\tan^{-1}(p_{xy}/p_{yy}) - \tan^{-1}(p_{yx}/p_{xx})$

The model gives results that make good use of a limited number of constellation samples. In addition, it neatly solves the question "What happens if the clusters do not lie on equally spaced parallel lines?" The model supplies a solution that will approximate the true constellation. It cannot be an exact fit if the constellation does not fit the linear model. However, the results are at least consistent, and

Fig. 8. Constellation best-fit model.

have low measurement variance. To determine the form and extent of nonlinear impairments, it is necessary to perform additional analysis in an external controller.

Notice in Fig. 8 that two of the corner clusters are slightly compressed towards the center of the constellation. The model gives more weight to the other fourteen clusters, so the lines do not pass through the centers of these corner clusters.

#### **Stand-Alone Operation**

All constellation measurement functions can be performed under HP-IB control. An external HP-IB controller can be programmed to collect constellation data for remote monitoring applications or to allow more extensive analysis.

During stand-alone operation, access to the HP 3709A's

measurement functions is provided by the **MEASURE** key on the front panel. When this key is pressed, the instrument accumulates statistics and displays the analysis results. This allows the operator to resolve small changes in the constellation which are often difficult to detect by eye. If an HP ThinkJet Printer is attached to the instrument, pressing the **PRINT** key will produce a report (Fig. 9) containing a copy of the constellation plus the analysis results. This can be filed to provide a permanent record, allowing a carrier organization to monitor long-term changes in the performance of its radio links.

#### **Acknowledgments**

Peter Roubaud developed the firmware for the HP 3709A HP-IB interface, including the PRINT function.

COMMENTS

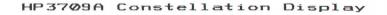

Fig. 9. HP 3709A constellation report printed on a Thinkjet Printer.

# **Authors**

July 1987

#### David J. Haworth

A project manager at the Queensferry Telecommunications Division, David Haworth has been with HP since 1972. He was responsible for the development of the HP 3709A Constellation Display, the HP 3717A 70-MHz Modulator/ Demodulator, and the HP

in electronics from Salford University in 1964 and is a specialist in high-frequency analog design, amplifiers, and oscillators. David is married and has two children. He likes photography and shares with Murdo McKissock an interest in Munro bagging

#### 13 Constellation Measurement

#### Murdo J. McKissock

With HP since 1981, Murdo McKissock worked on microprocessor and graphics hardware, constellation analysis, and instrument control firmware for the HP 3709A Constellation Display. He is named inventor for one patent application and coinventor for a sec-

ond application. Both are related to constellation measurement. Murdo is a graduate of the University of Manchester, Institute of Science and Technology (BSc electronics 1981). A resident of South Queensferry, Scotland, he enjoys bicycling, archery, cross-country skiing, and go. Another pastime is Munro bagging. (This means that he climbs Scottish mountains over 3,000 feet. Sir Hugh Munro published a table of such peaks in 1891.)

#### 19 Digital Radio Test Set

#### **Geoffrey Waters**

With HP's Queensferry Telecommunications Division since 1980, Geoff Waters is the R&D section manager responsible for developing instruments for testing broadband transmission systems. He was project manager for the HP 3708A Noise and Interfer-

ence Test Set. Before coming to HP he led an engineering group at Marconi Communication Systems, Ltd. that developed equipment for microwave radio links and satellite earth stations. Born in Sunderland, England, he earned a BSc degree in electrical engineering from the University of Newcastle upon Tyne in 1966. He has written several papers on diverse topics and is interested in the evolution of broadband fiber-optic-based telecommunication systems. Geoff and his wife and three children are residents of Edinburgh, Scotland. His favorite leisure activity is field archaeology, especially discovering unrecorded prehistoric sites. He also sings in a choral society and is learning to play traditional music on the piano accordion.

#### 26 Analog Power Meter

#### Anthony Lymer

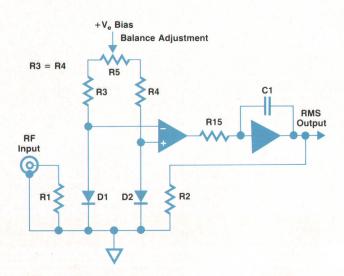

A 1975 graduate of the University College of North Wales, Tony Lymer holds a BSc degree in electrical and electronic engineering. He was a researcher at the University of Bath before coming to HP in 1982. He developed the rms-todc converter for the HP

3708A Test Set and more recently has worked on gate array design. He's coauthor of five articles on mobile radio modulation techniques and phaselocked loops and is a member of the Institution of Electronic and Radio Engineers. Born in Chelmsford, England, Tony is now a resident of Edinburgh, Scotland. Cross-country skiing and hiking head his list of leisure activities.

#### 30 - Noise Generator and Reference

#### Dayananda K. Rasaratnam

Daya Rasaratnam was born in Colombo, Sri Lanka and studied violin at the Royal College of Music, London (ARCM diploma 1975) before continuing his education in electrical and electronic engineering. He received a BSc degree from the University of Bir-

mingham in 1978 and joined HP the same year. An R&D engineer, he has contributed to the development of the HP 3724A Baseband Analyzer and the HP 3708A Test Set. At the same time, he was working toward an MSc degree in digital techniques from Heriot-Watt University and completed work for his degree in 1984. A resident of South Queensferry, Daya is married and has a young daughter. Music is an important outside interest. He participates in several orchestral concerts each year and plays duets with his wife for church meetings.

#### 36 Automated Radio Testing

#### John A. Duff

With HP since 1983, John Duff contributed to the development of the HP 3708S Measurement System and is currently working on a system for monitoring data lines. His professional specialty is workstation-based instrument control systems. He was born in Earley,

Berkshire, England and educated at the University of Southampton (BSc electronic engineering 1983). He now lives in Edinburgh, Scotland, is active in scouting, and is studying for an MBA degree. John likes all sports, especially white water canoeing, swimming, golf, and squash.

#### 4 Constellation Display

#### John R. Pottinger

John Pottinger holds a 1970 BSc degree in electronics from North Staffs Polytechnic Institute and a 1985 MSc degree from Heriot-Watt University. With HP since 1978, he contributed to the development of the HP 3724A, HP 3725A, and HP 3726A Baseband

Analyzers before working on analog and digital radio measurements and constellation analysis. He did the time base circuitry for the HP 3709A Constellation Display and is named coinventor on a patent application related to constellation analysis. Born in Reading, England, John now lives in Dunfermline, Scotland. He's married and has two children. His outside interests include gardening and mountain climbing, especially in challenging winter conditions.

#### Murdo J. McKissock

Author's biography appears elsewhere in this section

## A Digital Radio Noise and Interference Test Set

This instrument facilitates the measurement of the bit error ratio (BER) for a digital communication system under simulated path fade conditions. A desired C/N or C/I ratio can be established and maintained in the presence of received radio signal variations.

#### by Geoffrey Waters

**S** INCE THE LATE 1970s, an increasing proportion of long-haul telecommunications link equipment has used digital modulation techniques and this trend is expected to continue. Because of the nature of the error-generating mechanism in digital transmission, the accurate evaluation of a digital radio in terms of BER (bit error rate) versus C/N (carrier-to-noise) ratio requires a higher degree of measurement accuracy and repeatability than is required to evaluate an analog radio. Furthermore, the crest factor of the noise causing the errors assumes a more vital role. These factors initiated the development of the HP 3708A Noise and Interference Test Set (Fig. 1).

#### Establishing a C/N or C/No Ratio

The BER is usually measured over the range of C/N ratios encountered during hostile propagation conditions. The required C/N ratio is established either by varying the received signal level (RSL) by means of an attenuator (varying C) or by injecting additive noise into the receiver IF (varying N). Frequently in the laboratory, factory, or field, a variable RF attenuator is inserted into the microwave receiver input waveguide to attenuate the RSL. The thermal noise from the receiver's front end then defines the C/N<sub>o</sub> (carrier-tonoise-density) ratio according to:

$C/N_{o} = RSL + 174 - F at 17^{\circ}C$

where F is the noise figure of the receiver in dB and 174 dBm/Hz is the thermal noise floor at  $17^{\circ}$ C.

For example, assume the receiver noise figure is 6 dB and RSL is -70 dBm for a  $10^{-6}$  BER, then  $C/N_o = 98$  dB-Hz. This ratio remains unchanged throughout the receiver RF, IF, and predetection circuits because signal and noise are amplified equally. The typical unfaded  $C/N_o$  ratio would be about 40 dB higher, or 138 dB-Hz, and the BER would revert to a typical residual value of much less than  $10^{-10}$ . A 40-dB attenuator can be used to vary the  $C/N_o$  ratio from its unfaded value, allowing a BER curve to be plotted as a function of  $C/N_o$  ratio down to the receiver's threshold. Additional information on establishing a C/N or  $C/N_o$  ratio is given in reference 1.

Unlike C/N $_{\rm o}$ , the C/N ratio in the receiver varies at points throughout the RF/IF chain and depends on the appropriate noise bandwidth. That is:

$$C/N = C/N_o - 10 \log B_e$$

where  $\mathbf{B}_{\mathbf{e}}$  is the noise bandwidth at the point of interest. In terms of RSL:

$$C/N = RSL + 174 - F - 10 \log B_e$$

Using this equation, the C/N ratio can be related to the (continued on page 21)

**Fig. 1.** HP 3708A Noise and Interference Test Set for evaluating long-haul digital telecommunications systems.

-

1

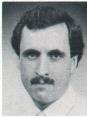

**Fig. 2.** Probability of symbol error versus C/N ratio for finite noise crest factor c for N-phase PSK (phase shift keying) data transmission and (b) QAM (quadrature amplitude modulation) data transmission.

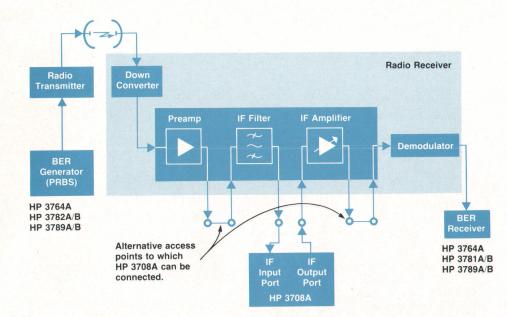

**Fig. 3.** Typical test configuration using HP 3708A Test Set.

RSL for the purposes of flat fade simulation. This method relies on knowing the noise bandwidth and noise figure for every radio under test. The sensitivity of the method to these values is unacceptably high, since BER can change by more than one order of magnitude for a C/N change of less than 0.5 dB.

The traditional method of fade simulation uses a power meter to check the effective C/N ratio in the receiver's IF strip or to measure the RSL at the RF stage. In the latter case, the levels are low and the nominal RSL is measured. The attenuator accuracy is relied on to set the desired RSL, assuming that the incoming signal level does not vary.

The RF attenuator method is time-consuming and inconvenient. In field tests, variations in RSL make it difficult or impossible to fade the RF signal as desired and make accurate BER measurements, particularly when working near receiver thresholds where a small scintillation fade can cause loss of synchronization.

Sometimes the inaccessibility of the waveguide attenuator makes the measurement slow, and it is difficult to automate. Matching problems and inherent attenuator inaccuracy at microwave frequencies reduce the reliability and repeatability of the measurements and increase the probability of operator error. There are too many uncontrolled variables for repeatable measurements.

Another method, the additive noise method, cannot check the overall fade margin but gives an accurate analysis of the C/N penalties caused by individual impairments in the radio. It is difficult and sometimes impossible to obtain this using the traditional method. The additive noise method establishes a C/N, C/N<sub>o</sub>, or  $E_b/N_o$  (energy/bit-tonoise-density) ratio by injecting relatively high-level noise into the receiver's demodulator or IF at normal RSL. The wideband noise spectral density of a noise generator is filtered to the desired bandwidth and supplied via an attenuator and amplifier combination to a network where it is combined with the IF carrier. The C/N ratio is established in the known noise bandwidth of the filter.

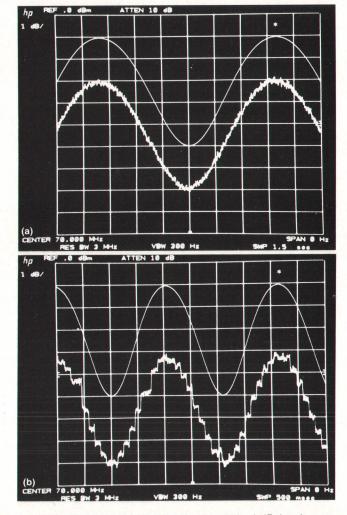

**Fig. 4.** Injected noise level versus variation in IF signal power. (a) Variation = 10 dB/s. (b) Variation = 50 dB/s. The top waveform in each plot is the sinusoidally varying carrier level and the bottom waveform is the averaged noise level.

## **Noise Crest Factor Enhancement**

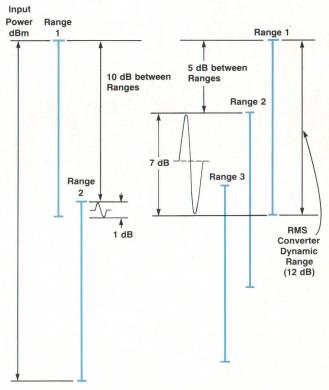

Crest factor is, by definition, the ratio of peak value to rms value. The noise crest factor at the noise output or the IF output of the HP 3708A is defined as the ratio of the hard-limiting voltage level to the rms value of the noise voltage. It has been shown<sup>1</sup> that the crest factor of noise used for determining bit error rate (BER) versus carrier-to-noise (C/N) ratio curves can significantly affect the accuracy of these curves for low BERs. Although a crest factor greater than 15 dB is sufficient to achieve good accuracy at BERs down to  $10^{-6}$ , it may sometimes be necessary to observe digital radio operation at significantly lower BERs.

The HP 3708A control algorithm in C/N mode makes it possible to have several different combinations of fine attenuator and step attenuator settings with a given carrier level and C/N ratio. This property can be exploited to enhance the noise crest factor at the IF output by exchanging attenuation between the fine attenuator and the step attenuators to reduce the level at the input to the final pair of amplifiers in the noise chain. The fine attenuator can, by this method, be set with a resolution of 1 dB to any part of its dynamic range provided that the resulting noise level at this output is  $\leq -10$  dBm and  $\geq -152$  dBm/Hz.\* The highest crest factor that can be so obtained is typically 25 dB.

The following general procedure lets the user establish a desired noise crest factor between 15 dB and 25 dB with a given carrier level and C/N ratio. Let the desired crest factor be k dB, where k is an integer such that  $15 \le k \le 25$ . Then:

- 1. Start with the desired C/N ratio as the current entry.

- 2. Enter desired C/N ratio incremented by  $\geq$ 12 dB.

- 3. Enter desired C/N ratio incremented by x dB, where x = 20 k. 4. Reenter desired C/N ratio (if x is not zero).

- \*Value in dBm is filter dependent

#### Reference

I. Young and G. Waters, "Practical Error Probability Estimation for Digital Radio Systems in the Presence of Interference and Noise of Finite Crest Factor, and the Prediction of Residual Error Rate," *IEE International Conference on Measurements for Telecommunication Transmission Systems—MTTS* 85, IEE, London, November 27-28, 1985.

> Dayananda K. Rasaratnam Development Engineer Queensferry Telecommunications Division

#### **Finite Crest Factor Noise**

The injected noise used in C/N testing must fulfill certain criteria: it must have sufficient bandwidth, a defined spectral density, and the correct statistics. The last requirement is frequently ignored.

The crest factor of a waveform is the ratio of the peak voltage to the rms value. An ideal Gaussian noise source process has infinitely high peaks. In other words, there is a finite chance that a peak as high as  $7\sigma$  will occur, even though this probability is only 1 in  $10^{12}$ . In practice the maximum noise output is constrained by power supply limitations. Gaussian noise with an infinite crest factor always produces a small but finite BER, no matter how large the C/N ratio is. However, when the crest factor is finite, reducing the noise below a certain threshold (or equivalently, raising the C/N ratio above a certain limit) makes the BER zero.

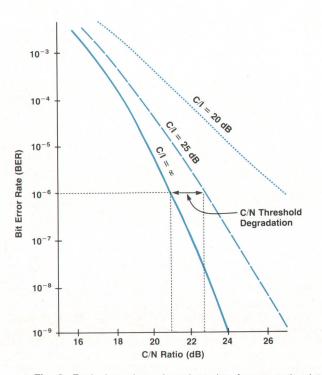

The theoretical probability of various symbol error rates has been computed for N-phase PSK (phase shift keying) and QAM (quadrature amplitude modulation) systems for various finite crest factors. The results are shown in Fig. 2. The effect of noise crest factor on the error rate can be seen together with the bound in C/N ratio discussed above where the error rate falls to zero. The crest factor should be high enough to allow accurate measurement at the appropriate BER. If this is not the case, the BER-versus-C/Nratio plot for the radio under test can deviate significantly from the theoretical curve, and different noise sources will produce different deviations. A critical factor in the design of the HP 3708A was to maximize the noise crest factor. Over the dynamic range of the instrument, typical values of 15 dB to 25 dB are achievable.

#### **HP 3708A Principles of Operation**

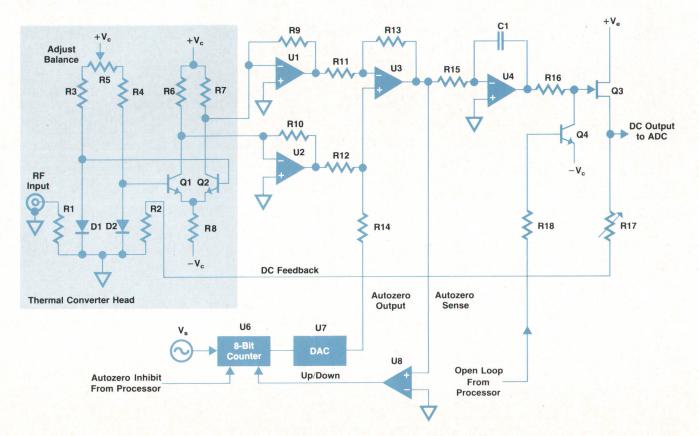

Two methods of establishing a C/N ratio have been described. The additive noise or noise injection method is used by the HP 3708A (see Fig. 3). Noise of known spectral density is injected into the IF section of the receiver under test to establish the desired carrier dependent ratio (C/N,

## **Noise Bandwidth Measurement**

The HP 3708A can measure the equivalent noise bandwidth of bandpass filters centered at 70 MHz or 140 MHz. This measurement is automatic except for one connection change. Other filters in the range of 10 to 200 MHz can be automatically measured after the insertion loss at the filter center frequency is entered into the HP 3708A.

The filter noise bandwidth (NBW) is the width in Hz of a rectangular filter that gives the same total noise power output as the actual filter, and has the same level of output noise density at the center frequency. An NBW of 10 MHz might be expressed as 70 dB-Hz where NBW (dB) = 10 log NBW (Hz). An NBW of 20 MHz would pass twice the power and would be given as 73 dB-Hz.

The HP 3708A measurement sequence starts with a gain or loss measurement of the filter under test at the band center frequency (70 MHz or 140 MHz). Using the gain or loss value and the input noise density, the HP 3708A calculates the output noise density at the center frequency. The total output power divided by this output noise density gives the NBW, which is then displayed on the front panel.

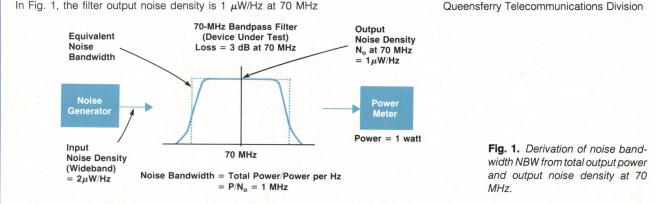

Fig. 1 shows a noise bandwidth calculation for a 70-MHz filter. In Fig. 1, the filter output noise density is 1  $\mu$ W/Hz at 70 MHz

and so a bandwidth of 1 MHz at this noise density must be postulated to account for the output power of 1 watt. The equivalent noise bandwidth is therefore 1 MHz. In this case the input noise density is 2  $\mu$ W/Hz since there is a 3-dB loss at the band center.

Fig. 1 also illustrates a method of measuring noise power density. When the output power, NBW, and loss of the filter are known, the input noise density can be calculated. For example, since the output power is 1 watt, the noise bandwidth is 1 MHz, and the loss at 70 MHz is 3 dB, the constant-level input noise density extending over the test-filter window must be 2  $\mu$ W/Hz.

The shape of the filter response is not critical. The filter and power meter represent a black box. This method is used to measure the output noise density of the HP 3708A in production test. Periodic calibration of the filter and power meter combination to find the relation between input noise density and power meter reading is carried out by a computer-controlled routine using a signal generator, a power meter, and numerical integration.

Ian M. Matthews

**Development Engineer**

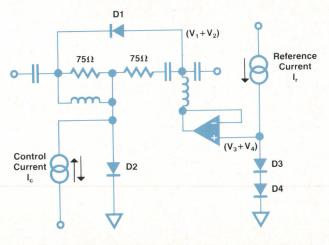

$C/N_o$ , or  $E_b/N_o$ ). The receiver IF power is measured at the point of noise injection, and the noise density is adjusted automatically under microprocessor control to maintain the required carrier dependent ratio in the presence of received signal level variations. The typical instrument response time is 10 ms, which enables BER testing to be performed in the field in the presence of rapid changes in RSL. Fig. 4 shows the injected noise tracking sinusoidal variations in IF signal power at 50 dB/s and 10 dB/s. Because the carrier power is measured at the point of noise injection, the required carrier dependent ratio is maintained at any point chosen for noise injection throughout the IF chain.

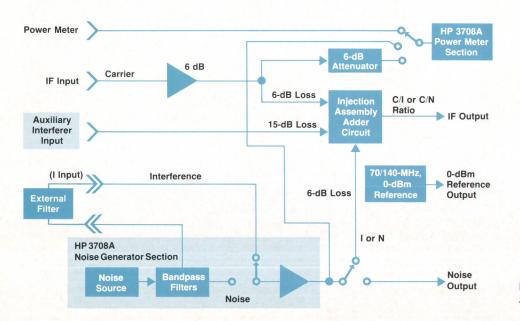

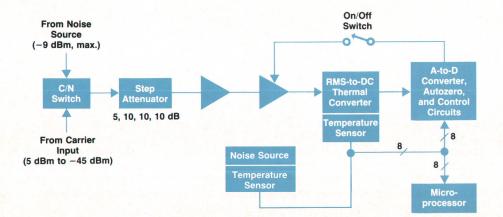

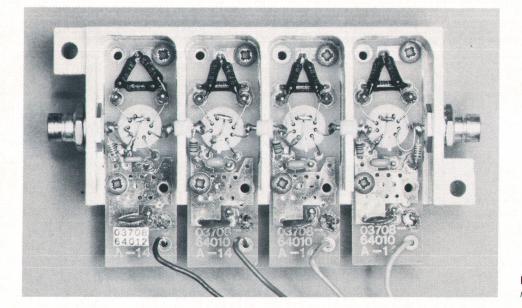

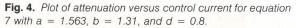

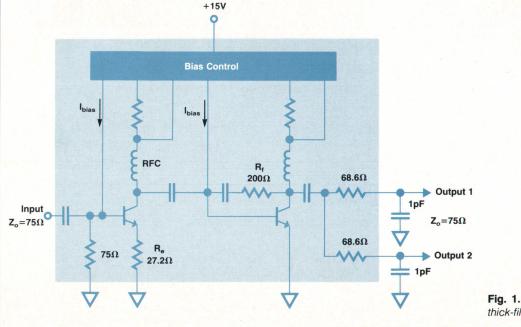

The block diagram of the instrument consists of a power meter, a noise source, an injection assembly, and a microprocessor (Fig. 5). To this is added a 0-dBm reference source, an HP-IB (IEEE 488/IEC 625) port, and a power supply.

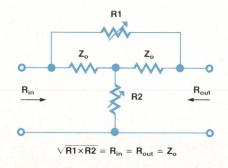

The user's radio signal is passed through the injection assembly via the HP 3708A's IF input and output ports. The injection assembly has 0-dB loss and negligible transmission impairments to carrier powers as high as 5 dBm.

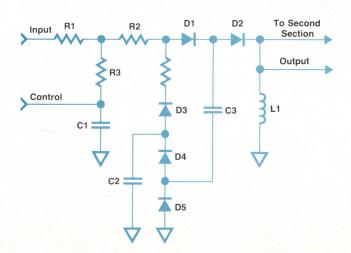

Noise injection is controlled by a switched attenuator

and a continuously variable pin diode attenuator in the noise source. When a requested C/N ratio is established, the microprocessor sets the switched attenuator so that the pin diode attenuator is in the middle of its range. This allows a rapid variation of the noise level over  $\pm 5$  dB without operating the switched attenuator, which ensures fast response to carrier variations. In some special applications this noise tracking facility is not required and a track inhibit mode of operation is available.

The HP 3708A can be used to test TDMA (time division multiple access) burst mode systems. The carrier power is measured with an external burst mode power meter and entered into the HP 3708A using the **ENTER C** data entry key in track inhibit mode.

#### **Special Features**

Three ratios are available on the HP 3708A: carrier-tonoise ratio, carrier-to-noise-density ratio, and energy/bit-tonoise-density ratio. The last two ratios are independent of bandwidth and are particularly useful in R&D work for comparing the efficiency of different radio systems. These measurements require an accurately known noise density for injection into the radio's IF section. The concept of  $E_b/N_o$  ratio results in a figure of merit for comparing systems that emphasizes the minimization of the total transmitted energy required to convey a given amount of data.  $E_b$  is obtained by dividing the carrier power C by the bit rate  $f_b$ . Therefore,  $E_b/N_o=(C/f_b)(1/N_o)$ , or in dB,  $E_b/N_o=C/N_o-10 \log f_b$ .

After measuring the IF carrier power, the HP 3708A must know the transmission bit rate of the system under test to inject the appropriate noise density to establish a required  $E_b/N_o$ . This can be entered via the data entry keys on the front panel. If the receiver noise bandwidth is  $B_e$  Hz and the total noise power measured in this bandwidth is N watts, then  $N_o = N/B_e$  watts/Hz. Hence,  $E_b/N_o = (C/N)$  ( $B_e/f_b$ ), or in dB,  $E_b/N_o = C/N - 10 \log f_b/B_e$ . Therefore, if the noise bandwidth equals the bit rate,  $E_b/N_o = C/N$ .

The measurement of the BER of a system at a particular C/N ratio must be related to a specified system bandwidth (e.g., the noise bandwidth of practical receiver filters) or to the theoretical minimum Nyquist bandwidth (symbol rate bandwidth). Therefore, a system bandwidth key is associated with the C/N data entry key on the HP 3708A. This allows noise of appropriate noise density to be injected at a convenient point in the radio's IF section to establish a required C/N ratio at another point (e.g., downstream in the bandwidth of the baseband filters at the regenerator input).

The HP 3708A operates at common microwave receiver IF bands from 10.7 MHz to 140 MHz. The injected noise is band limited in the range of 10 MHz to 200 MHz by a choice of four internal filters or by connecting an external filter of the operator's choosing. To ensure that the injected noise density is calibrated, the noise bandwidth of each filter in each instrument is individually measured and stored as a soft constant.

Because the HP 3708A contains an accurate noise source, an IF power meter, and a microprocessor, the instrument can be configured to measure the noise bandwidth of an external filter in seconds, thus avoiding the lengthy numerical integration procedures normally used (see "Noise Bandwidth Measurement," page 23). To increase the instrument's flexibility, both its internal power meter and its noise source are accessible from the front panel for more general-purpose applications.

#### Additive Interference Testing

The HP 3708A offers two distinct facilities for interference testing. Aimed at different applications, both facilities have broadband inputs with a frequency range of 10 MHz to 200 MHz.

Co-channel and adjacent channel interference effects influence the design of radio hardware and are of interest to the frequency planner and regulatory agencies. These effects can have a predominating influence on the BER performance of a radio. It is common practice to measure the C/N threshold degradation that occurs in the presence of interference over a range of co-channel and adjacent channel frequencies. Fig. 6 shows a typical co-channel C/I (carrier-to-interference) plot for an 8-phase PSK radio. The degradation in threshold can be seen clearly.

To simplify this measurement, the HP 3708A has an auxiliary interferer input on its rear panel with a fixed loss to the HP 3708A's IF output port of typically 15 dB. The required C/N ratio is established via the keyboard in the normal manner and the C/I ratio is determined by the level presented to the auxiliary interferer input. In this mode of

**Fig. 6.** Typical co-channel carrier-to-interference ratio plot for an 8-phase PSK radio.

**Fig. 7.** C/N ratio repeatability for HP 3708A measurements at 70±20 MHz.

operation the established C/N ratio is independent of variations in received carrier power, but the C/I ratio is not.

An external source of interference (modulated or unmodulated) can be used or the internal 0-dBm calibrator (normally at 70 MHz and 140 MHz) can be substituted.

Because of a growing interest in deterministic testing of QAM radio systems (rather than statistical testing with noise), the C/I mode of the HP 3708A allows the injection of a noise-free additive sinusoidal tone. In this mode of operation the automatic leveling algorithm maintains the C/I ratio in the presence of received signal level variations. The interferer is connected to the input port on the instrument's front panel.

The residual BER of a radio system at nominal received signal level is practically impossible to measure because the mean time between errors can be from tens to hundreds of hours. The C/I ratio required to establish a specific BER depends on the amount of intersymbol interference and residual noise present around the phase states in the constellation display. The estimation of this C/I ratio can be used to predict the residual, or dribble, BER for a radio system. This technique is described in reference 2.

Measurement of residual BER can now be made in minutes as opposed to the three days previously required to wait for 30 errors (100 Mbits/s, BER =  $10^{-12}$ ). Measurement

Fig. 8. Linearity of internal HP 3708A power meter over 1240 measurements.

of residual BER is now feasible in the field and test time can be saved in production, allowing repeated tests to be made for evaluation of adjustments.

#### Self Calibration Enhances Accurate Operation

When measuring the fade margins of a microwave radio system, the accuracy with which the C/N ratio can be specified is of vital importance. This is primarily because the slope of the BER-versus-C/N-ratio curve is so steep that less than a 0.5-dB change in C/N ratio can result in one order of magnitude variation in BER. Hence, the HP 3708A uses a powerful 16-bit microprocessor to implement sophisticated calibration procedures that enable a C/N or C/I ratio to be established to a typical accuracy of 0.1 dB at room temperatures.

Each signal path in the HP 3708A and the noise bandwidths of the noise defining filters are characterized by individually measured software constants. This calibration data is held in nonvolatile memory. The exact values are determined for each instrument during production test to achieve maximum accuracy. Thirty-three soft constants are stored in each HP 3708A. These constants are:

- 1. RF path gains and losses

- 2. Filter noise bandwidths

- 3. Measured attenuator incremental attenuation values.

A temperature sensor ensures that an autocalibration cycle is initiated should the noise source temperature change by 3°C or more.

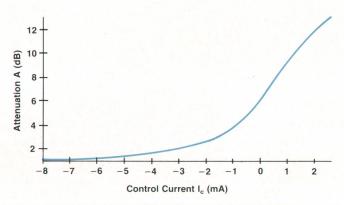

The power meter can be calibrated using the accurate internal 0-dBm source described in the article on page 30, and subsequent measurements are referred to this level.